New RISC-V hardware designs from 5G startup EdgeQ

-

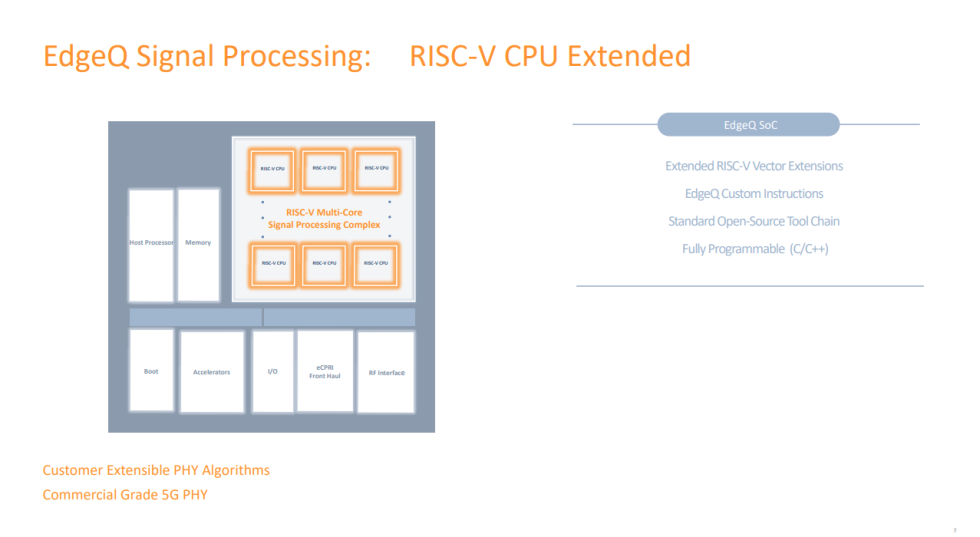

This is a diagram of an entire host board. EdgeQ's extended RISC-V CPU is on the upper right; "Host Processor" on the left is the CPU the Linux OS would actually run on. [credit: EdgeQ ]

Today, 5G cellular startup EdgeQ is announcing the addition of two new members to its advisory board—former Qualcomm CEO Paul Jacobs, and former Qualcomm CTO Matt Grob. Their mission is to cut the Total Cost of Ownership (TCO) of 5G cellular base stations in half by leveraging and extending open hardware RISC-V designs.

Traditionally, Radio Access Network (RAN) devices have tended to be closed design and deeply proprietary—much like consumer Wi-Fi and network hardware, they depend on closed-design ASICs with vendor-provided drivers and firmware. Such closed stacks generally cannot be upgraded to accommodate new protocols and use cases—for example, a Radio Unit or Distributed Unit designed for 4G networks must typically be replaced in its entirety in order to service 5G devices.

By contrast, vendors can implement their own OpenRAN solutions, which generally implement fewer functions in hardware, and more in software running on traditional operating systems such as Linux. But implementing such an O-RAN properly requires very deep protocol expertise to get right, and it tends to be extremely power-hungry and expensive to maintain once finished.

Read 5 remaining paragraphs | Comments

from Tech – Ars Technica https://ift.tt/3iNdvBa

Comments

Post a Comment